# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111180379 A (43)申请公布日 2020.05.19

**B82Y 40/00**(2011.01)

(21)申请号 201911367573.7

(22)申请日 2019.12.26

(71)申请人 华灿光电(苏州)有限公司 地址 215600 江苏省苏州市张家港市经济 开发区晨丰公路

(72)发明人 兰叶 吴志浩 李鹏

(74) 专利代理机构 北京三高永信知识产权代理 有限责任公司 11138

代理人 吕耀萍

(51) Int.CI.

**H01L 21/683**(2006.01)

H01L 33/00(2010.01)

H01L 33/62(2010.01)

H01L 33/06(2010.01)

H01L 33/32(2010.01)

权利要求书2页 说明书8页 附图7页

#### (54)发明名称

微型发光二极管外延片、显示阵列及其制作 方法

#### (57)摘要

本公开提供了一种微型发光二极管外延片、显示阵列及其制作方法,属于半导体技术领域。制作方法包括:提供半导体器件,半导体器件包括衬底和在衬底的第一表面上间隔设置的多个发光单元,衬底的第一表面上两点之间的最大距离为0.2mm~1mm;将半导体器件转移到电路板上,每个发光单元中的P型电极键合在电路板的第一表面上;依次去除衬底和每个发光单元中的缓冲层,并在每个发光单元中的电子产生层上设置N型电极,形成发出第一颜色光线的芯片;分别在不同的芯片上设置第一荧光粉层和第二荧光粉层,第一荧光粉层将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为

CN 111180379

1.一种微型发光二极管显示阵列的制作方法,其特征在于,所述制作方法包括:

提供半导体器件,所述半导体器件包括衬底和在所述衬底的第一表面上间隔设置的多个发光单元,每个所述发光单元包括依次层叠在所述衬底的第一表面上的缓冲层、电子产生层、有源层、空穴产生层和P型电极,所述衬底的第一表面上两点之间的最大距离为0.2mm~1mm;

将所述半导体器件转移到电路板上,每个所述发光单元中的P型电极键合在所述电路板的第一表面上:

依次去除所述衬底和每个所述发光单元中的缓冲层,并在每个所述发光单元中的电子 产生层上设置N型电极,形成发出第一颜色光线的芯片;

分别在不同的所述芯片上设置第一荧光粉层和第二荧光粉层,所述第一荧光粉层将所述第一颜色光线转换为第二颜色光线,所述第二荧光粉层将所述第一颜色光线转换为第三颜色光线。

2.根据权利要求1所述的制作方法,其特征在于,所述电路板的第一表面上设有与所述 半导体器件一一对应的定位柱,所述定位柱平行于所述电路板的第一表面的截面的面积向 远离所述电路板的第一表面的方向逐渐增大;

所述将所述半导体器件转移到电路板上,每个所述发光单元中的P型电极键合在所述 电路板的第一表面上,包括:

将所述半导体器件放置在所述电路板的第一表面上,直到所述半导体器件中的P型电极与所述电路板的第一表面相贴;

沿平行于所述电路板的第一表面的方向移动所述半导体器件,直到所述半导体器件与 所述半导体器件对应的定位柱相抵:

将所述半导体器件和所述电路板键合在一起。

3.根据权利要求1或2所述的制作方法,其特征在于,所述有源层包括交替层叠的多个量子阱和多个量子垒,每个所述量子阱采用如下方式生长:

梯度增大通入反应腔内In源的流量,生长第一InGaN层,所述第一InGaN层的势垒高度沿生长方向梯度减小;

保持通入反应腔内In源的流量不变,生长第二InGaN层,所述第二InGaN层的势垒高度保持不变;

梯度减小通入反应腔内In源的流量,生长第三InGaN层,所述第三InGaN层的势垒高度沿生长方向梯度增大,所述第一InGaN层、所述第二InGaN层和所述第三InGaN层组成量子阱。

4.根据权利要求3所述的制作方法,其特征在于,在通入反应腔内In源的流量增大时, In源流量的增大速率逐渐增大,使所述第一InGaN层的势垒高度减小处呈圆弧状;

在通入反应腔内In源的流量减小时,In源流量的减小速率逐渐减小,使所述第三InGaN层的势垒高度增大处呈圆弧状。

- 5.根据权利要求3所述的制作方法,其特征在于,每个所述量子垒采用如下方式生长: 向反应腔内通入A1源,生长A1GaN层。

- 6.一种微型发光二极管显示阵列,其特征在于,所述微型发光二极管显示阵列包括电路板(10)、多个芯片(20)、第一荧光粉层(31)和第二荧光粉层(32),所述多个芯片(20)间隔

设置在所述电路板(10)的第一表面上,每个所述芯片(20)包括依次层叠在所述电路板(10)的第一表面上的P型电极(21)、空穴产生层(22)、有源层(23)、电子产生层(24)和N型电极(25),所述第一荧光粉层(31)和所述第二荧光粉层(32)分别设置在不同的所述芯片(20)上,所述芯片(20)发出第一颜色光线,所述第一荧光粉层(31)将所述第一颜色光线转换为第二颜色光线,所述第二荧光粉层(32)将所述第一颜色光线转换为第三颜色光线。

- 7.根据权利要求6所述的微型发光二极管显示阵列,其特征在于,所述电路板(10)的第一表面上设有定位柱(11),所述定位柱(11)平行于所述电路板(10)的第一表面的截面的面积向远离所述电路板(10)的第一表面的方向逐渐增大。

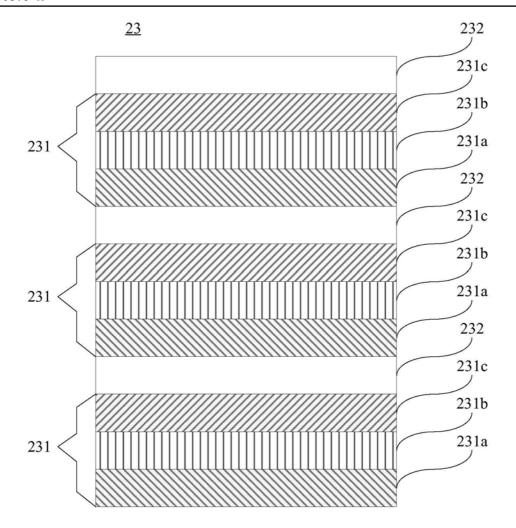

- 8.根据权利要求6或7所述的微型发光二极管显示阵列,其特征在于,所述有源层(23)包括交替层叠的多个量子阱(231)和多个量子垒(232),每个所述量子阱(231)包括依次层叠的第一InGaN层(231a)、第二InGaN层(231b)和第三InGaN层(231c),所述第一InGaN层(231a)的势垒高度沿生长方向梯度减小,所述第二InGaN层(231b)的势垒高度保持不变,所述第三InGaN层(231c)的势垒高度沿生长方向梯度增大。

- 9.根据权利要求8所述的微型发光二极管显示阵列,其特征在于,所述第一InGaN层 (231a)的势垒高度减小处呈圆弧状,所述第三InGaN层 (231c)的势垒高度增大处呈圆弧状。

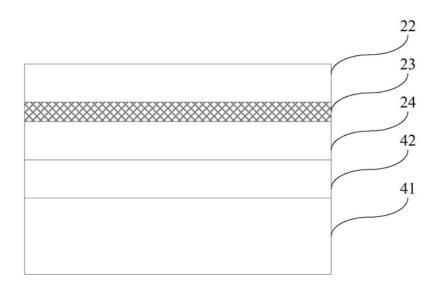

- 10.一种微型发光二极管外延片,其特征在于,所述微型发光二极管外延片包括衬底 (41) 和依次层叠在所述衬底 (41) 上的缓冲层 (42)、电子产生层 (24)、有源层 (23) 和空穴产生层 (22),所述有源层 (23) 包括交替层叠的多个量子阱 (231) 和多个量子垒 (232),每个所述量子阱 (231) 包括依次层叠的第一InGaN层 (231a)、第二InGaN层 (231b) 和第三InGaN层 (231c),所述第一InGaN层 (231a)的势垒高度沿生长方向梯度减小,所述第二InGaN层 (231b)的势垒高度保持不变,所述第三InGaN层 (231c)的势垒高度沿生长方向梯度增大。

# 微型发光二极管外延片、显示阵列及其制作方法

#### 技术领域

[0001] 本公开涉及半导体技术领域,特别涉及一种微型发光二极管外延片、显示阵列及其制作方法。

### 背景技术

[0002] 发光二极管(英文:Light Emitting Diode,简称:LED)是一种常用的发光器件,通过电子与空穴复合释放能量发光,广泛地应用在日常生活中的显示、装饰、通讯和照明等领域。通过采用不同的半导体材料和结构,发光二极管能够覆盖从紫外到红外的全色范围,基本占据了室内和室外的大间距显示器市场。其中,间距是指显示器中相邻两个显示单元之间的距离,与显示器的分辨率有关。

[0003] 当前小间距显示器市场仍以液晶显示器(英文:Liquid Crystal Display,简称:LCD)为主流。虽然有机发光二极管(英文:Organic Light-Emitting Diode,简称:OLED)正在某些领域替代LCD成为主流,但是OLED存在烧屏等问题。微型发光二极管(英文:Micro LED)是指边长在10微米~100微米的超小型发光二极管,体积小,可以更密集地排列在一起而大幅提高分辨率,并且具有自发光特性,在高亮度、高对比度、快速反应和省电等方面都优于LCD和OLED,未来很可能会进一步占据小间距显示器市场。

[0004] 显示阵列是小间距显示器和大间距显示器的基本结构。相关技术中,Micro LED的显示阵列包括电路板和转移到电路板上的多个芯片。Micro LED芯片的尺寸很小,密集布置在电路板上,对转移的精度要求较高。而且Micro LED芯片的转移数量随尺寸的减小以级数上升,已达到巨量的规模,需要由设备统一进行转移。但是转移设备的吸嘴直径很难做到比Micro LED芯片的尺寸更小,无法提供足够的吸力转移Micro LED芯片。

### 发明内容

[0005] 本公开实施例提供了一种微型发光二极管外延片、显示阵列及其制作方法,可以增大单次转移的芯片规模,适应转移设备的吸嘴直径,可以提供足够的吸力转移Micro LED 芯片。所述技术方案如下:

[0006] 一方面,本公开实施例提供了一种微型发光二极管显示阵列的制作方法,所述制作方法包括:

[0007] 提供半导体器件,所述半导体器件包括衬底和在所述衬底的第一表面上间隔设置的多个发光单元,每个所述发光单元包括依次层叠在所述衬底的第一表面上的缓冲层、电子产生层、有源层、空穴产生层和P型电极,所述衬底的第一表面上两点之间的最大距离为0.2mm~1mm;

[0008] 将所述半导体器件转移到电路板上,每个所述发光单元中的P型电极键合在所述电路板的第一表面上:

[0009] 依次去除所述衬底和每个所述发光单元中的缓冲层,并在每个所述发光单元中的电子产生层上设置N型电极,形成发出第一颜色光线的芯片:

[0010] 分别在不同的所述芯片上设置第一荧光粉层和第二荧光粉层,所述第一荧光粉层 将所述第一颜色光线转换为第二颜色光线,所述第二荧光粉层将所述第一颜色光线转换为 第三颜色光线。

[0011] 可选地,所述电路板的第一表面上设有与所述半导体器件一一对应的定位柱,所述定位柱平行于所述电路板的第一表面的截面的面积向远离所述电路板的第一表面的方向逐渐增大;

[0012] 所述将所述半导体器件转移到电路板上,每个所述发光单元中的P型电极键合在 所述电路板的第一表面上,包括:

[0013] 将所述半导体器件放置在所述电路板的第一表面上,直到所述半导体器件中的P型电极与所述电路板的第一表面相贴;

[0014] 沿平行于所述电路板的第一表面的方向移动所述半导体器件,直到所述半导体器件与所述半导体器件对应的定位柱相抵;

[0015] 将所述半导体器件和所述电路板键合在一起。

[0016] 可选地,所述有源层包括交替层叠的多个量子阱和多个量子垒,每个所述量子阱采用如下方式生长:

[0017] 梯度增大通入反应腔内In源的流量,生长第一InGaN层,所述第一InGaN层的势垒高度沿生长方向梯度减小;

[0018] 保持通入反应腔内In源的流量不变,生长第二InGaN层,所述第二InGaN层的势垒 高度保持不变:

[0019] 梯度减小通入反应腔内In源的流量,生长第三InGaN层,所述第三InGaN层的势垒高度沿生长方向梯度增大,所述第一InGaN层、所述第二InGaN层和所述第三InGaN层组成量子阱。

[0020] 可选地,在通入反应腔内In源的流量增大时,In源流量的增大速率可以逐渐增大,使所述第一InGaN层的势垒高度减小处呈圆弧状:

[0021] 在通入反应腔内In源的流量减小时,In源流量的减小速率可以逐渐减小,使所述第三InGaN层的势垒高度增大处呈圆弧状。

[0022] 可选地,每个所述量子垒采用如下方式生长:

[0023] 向反应腔内通入A1源,生长A1GaN层。

[0024] 另一方面,本公开实施例提供了一种微型发光二极管显示阵列,所述微型发光二极管显示阵列包括电路板、多个芯片、第一荧光粉层和第二荧光粉层,所述多个芯片间隔设置在所述电路板的第一表面上,每个所述芯片包括依次层叠在所述电路板的第一表面上的P型电极、空穴产生层、有源层、电子产生层和N型电极,所述第一荧光粉层和所述第二荧光粉层分别设置在不同的所述芯片上,所述芯片发出第一颜色光线,所述第一荧光粉层将所述第一颜色光线转换为第二颜色光线,所述第二荧光粉层将所述第一颜色光线转换为第三颜色光线。

[0025] 可选地,所述电路板的第一表面上设有定位柱,所述定位柱平行于所述电路板的第一表面的截面的面积向远离所述电路板的第一表面的方向逐渐增大。

[0026] 可选地,所述有源层包括交替层叠的多个量子阱和多个量子垒,每个所述量子阱包括依次层叠的第一InGaN层、第二InGaN层和第三InGaN层,所述第一InGaN层的势垒高度

沿生长方向梯度减小,所述第二InGaN层的势垒高度保持不变,所述第三InGaN层的势垒高度沿生长方向梯度增大。

[0027] 可选地,所述第一InGaN层的势垒高度减小处呈圆弧状,所述第三InGaN层的势垒高度增大处呈圆弧状。

[0028] 又一方面,本公开实施例提供了一种微型发光二极管外延片,所述微型发光二极管外延片包括衬底和依次层叠在所述衬底上的缓冲层、电子产生层、有源层和空穴产生层,所述有源层包括交替层叠的多个量子阱和多个量子垒,每个所述量子阱包括依次层叠的第一InGaN层、第二InGaN层和第三InGaN层,所述第一InGaN层的势垒高度沿生长方向梯度减小,所述第二InGaN层的势垒高度保持不变,所述第三InGaN层的势垒高度沿生长方向梯度增大。

[0029] 本公开实施例提供的技术方案带来的有益效果是:

[0030] 通过将多个发光单元集成在同一个衬底上一起转移到电路板上,衬底设置发光单元的表面上两点之间的最大距离为0.2mm~1mm,将转移的半导体器件的尺寸增大至比转移设备的吸嘴直径大,可以解决转移设备的吸嘴直径不能比Micro LED芯片的尺寸小的问题,使得转移设备可以提供足够的吸力转移Micro LED芯片。而且衬底设置发光单元的表面上两点之间的最大距离为0.2mm~1mm,设置在衬底上发光单元的数量较少,有利于保证设置位置的精确度。另外,多个发光单元一起转移到电路板上,可以减少转移的数量,降低加工成本。

# 附图说明

[0031] 为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

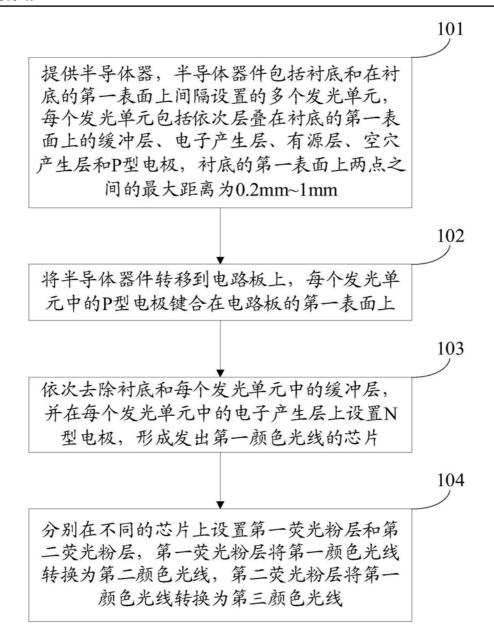

[0032] 图1是本公开实施例提供的一种微型发光二极管显示阵列的制作方法的结构示意图:

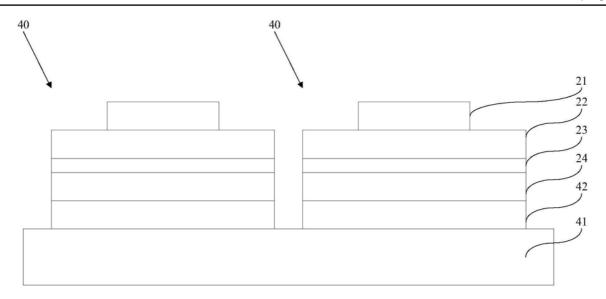

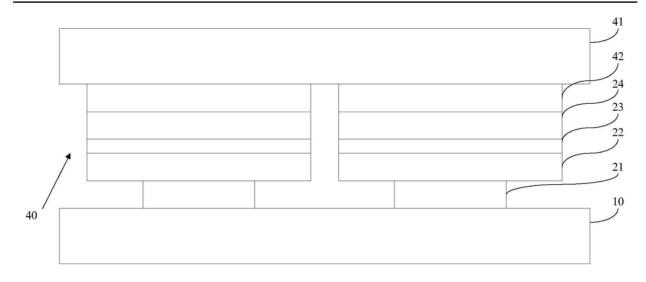

[0033] 图2是本公开实施例提供的显示阵列在执行步骤101之后的结构示意图:

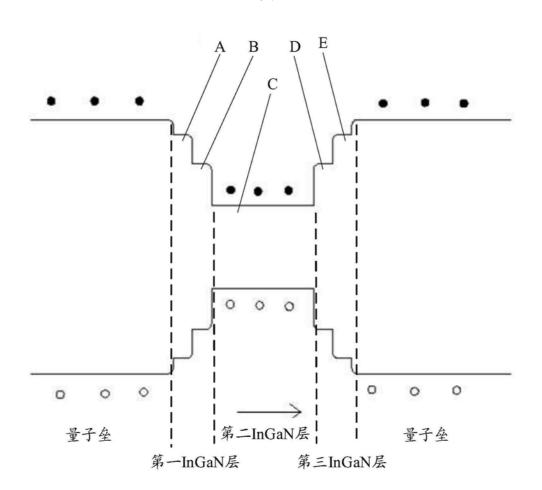

[0034] 图3是本公开实施例提供的量子垒的势垒高度的结构示意图:

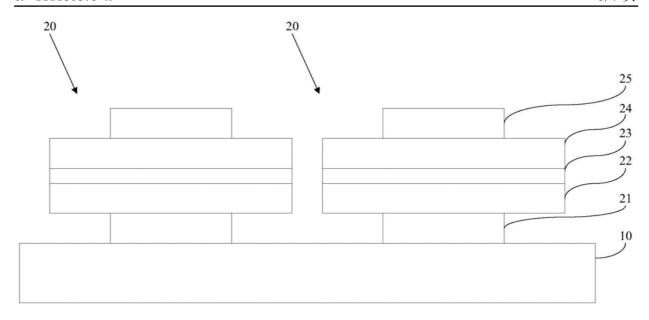

[0035] 图4是本公开实施例提供的显示阵列在执行步骤102之后的结构示意图:

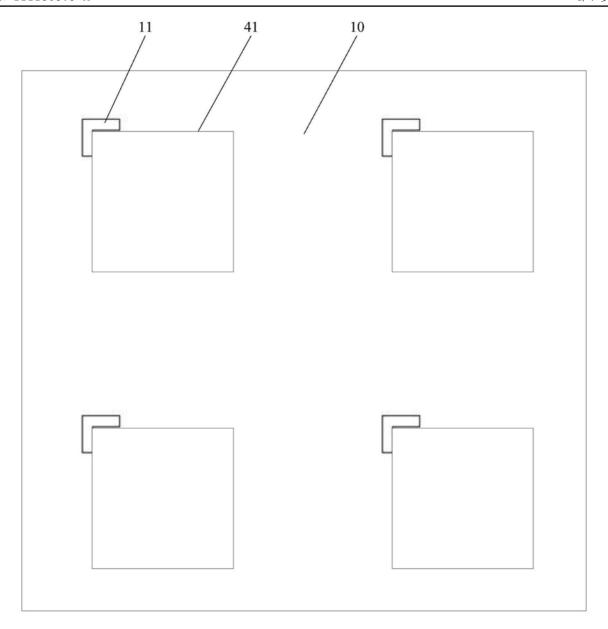

[0036] 图5是本公开实施例提供的显示阵列在步骤102之后的俯视图;

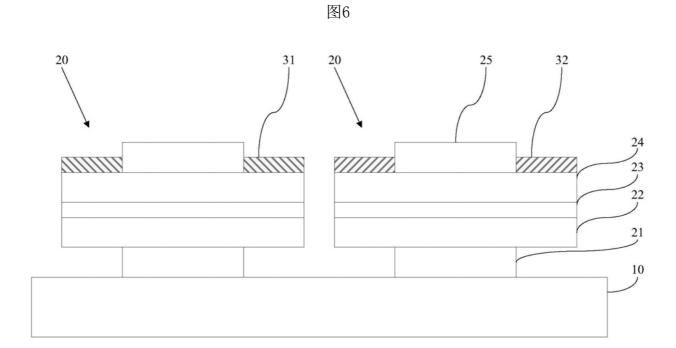

[0037] 图6是本公开实施例提供的显示阵列在执行步骤103之后的结构示意图;

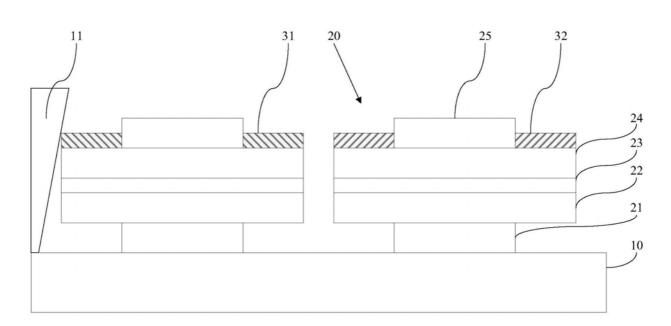

[0038] 图7是本公开实施例提供的显示阵列在执行步骤104之后的结构示意图:

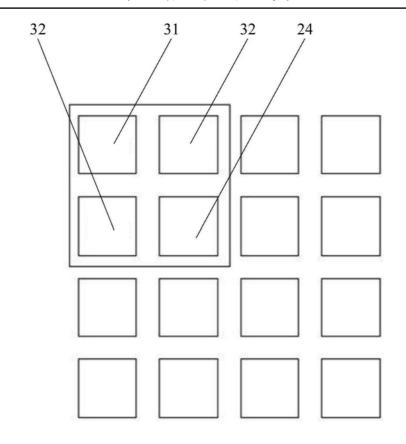

[0039] 图8是本公开实施例提供的显示阵列在执行步骤104之后的俯视图:

[0040] 图9是本公开实施例提供的一种微型发光二极管显示阵列的结构示意图:

[0041] 图10是本公开实施例提供的有源层的结构示意图;

[0042] 图11是本公开实施例提供的一种微型发光二极管外延片的结构示意图。

### 具体实施方式

[0043] 为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方

式作进一步地详细描述。

[0044] 本公开实施例提供了一种微型发光二极管显示阵列的制作方法。图1为本公开实施例提供的一种微型发光二极管显示阵列的制作方法的结构示意图。参见图1,该制作方法包括:

[0045] 步骤101:提供半导体器,半导体器件包括衬底和在衬底的第一表面上间隔设置的多个发光单元,每个发光单元包括依次层叠在衬底的第一表面上的缓冲层、电子产生层、有源层、空穴产生层和P型电极,衬底的第一表面上两点之间的最大距离为0.2mm~1mm。

[0046] 图2为本公开实施例提供的显示阵列在执行步骤101之后的结构示意图。参见图2,两个发光单元40间隔设置在衬底41的同一个表面上,即衬底41的第一表面。每个发光单元40包括依次层叠的缓冲层42、电子产生层24、有源层23、空穴产生层22和P型电极21。

[0047] 在实际应用中,多个发光单元可以以阵列方式布置在衬底的第一表面上,如4\*4的阵列、6\*6的阵列、8\*8的阵列、12\*12的阵列、20\*20的阵列等。

[0048] 优选地,衬底的第一表面上两点之间的最大距离为0.6mm。目前外延层的尺寸一般为0.05mm~1mm,转移设备喷嘴的最佳直径一般为0.2mm~2mm,衬底的第一表面上两点之间的最大距离可以兼顾这两个取值范围。

[0049] 示例性地,衬底的材料可以采用蓝宝石、砷化镓、磷化镓、碳化硅、氧化锌、氮化硅和玻璃中的一种,衬底的厚度可以减薄至100微米。缓冲层的材料可以采用GaN,厚度可以为0.5微米以上,远大于常规的0.1微米以下,以避免激光剥离时产生的应力影响到外延层。电子产生层的材料可以采用掺硅的GaN,空穴产生层的材料可以采用掺镁的GaN。P型电极可以包括依次层叠的铬层和金层,金层的厚度在2微米以上。

[0050] 可选地,该步骤101可以包括:

[0051] 第一步,在衬底的第一表面上依次生长缓冲层、电子产生层、有源层和空穴产生层;

[0052] 第二步,在空穴产生层上间隔设置多个P型电极;

[0053] 第三步,在空穴产生层上开设延伸至衬底的隔离槽,形成与多个P型电极一一对应的多个发光单元。

[0054] 在实际应用中,在第一步中,可以采用金属有机化合物化学气相沉淀(英文: Metal-organic Chemical Vapor Deposition,简称:MOCVD)技术外延生长缓冲层、电子产生层、有源层和空穴产生层。示例性地,缓冲层的生长温度可以为300℃,以实现低温生长。

[0055] 在第二步中,可以采用物理气相沉积(英文:Physical Vapor Depositon,简称: PVD) 技术(如蒸发、溅射等) 铺设金属形成P型电极。

[0056] 在第三步中,可以先采用光刻技术在空穴产生层上形成图形化的光刻胶,再采用刻蚀技术在空穴产生层上形成延伸至衬底的隔离槽,最后去除光刻胶即可。

[0057] 可选地,在第一步之前,可以采用KOH溶液粗化蓝宝石衬底,以缓解外延生长过程中的晶格失配,提高晶体质量。

[0058] 在第一步之后,可以通过短时间内高温生长形成接触层。

[0059] 在本实施例中,有源层包括交替层叠的多个量子阱和多个量子垒。示例性地,量子阱的数量可以为5个,以避免外延层太厚而影响到Micro LED的应用。

[0060] Micro LED中量子阱的数量较小,各个量子阱中载流子的数量较多,载流子在移动

过程中会对量子阱的侧壁产生较大的冲击,破坏量子阱两侧的量子垒晶格,导致量子垒无法将载流子限制在量子阱中进行复合发光,影响发光效率。

[0061] 可选地,每个量子阱可以采用如下方式生长:

[0062] 第一步,梯度增大通入反应腔内In源的流量,生长第一InGaN层,第一InGaN层的势垒高度沿生长方向梯度减小;

[0063] 第二步,保持通入反应腔内In源的流量不变,生长第二InGaN层,第二InGaN层的势垒高度保持不变;

[0064] 第三步,梯度减小通入反应腔内In源的流量,生长第三InGaN层,第三InGaN层的势垒高度沿生长方向梯度增大,第一InGaN层、第二InGaN层和第三InGaN层组成量子阱。

[0065] 在实际应用中,向反应腔内通入In源、Ga源和N源,并控制温度、压力等条件,即可生长InGaN层。通入反应腔内In源的流量越大,InGaN层中In组分的含量越高,InGaN层的势垒越低。

[0066] 本公开实施例通过在InGaN层刚开始生长的时候,梯度增大通入反应腔内In源的流量,使得InGaN层的势垒高度呈阶梯式减小,同时在InGaN层快结束生长的时候,梯度减小通入反应腔内In源的流量,使得InGaN的势垒高度呈阶梯式增大,这样整个量子阱的势垒高度呈现中间低、两端逐渐增高的状态,使得载流子能够较为平缓地通过量子阱,有效减缓量子阱对量子垒晶格的冲击,量子垒可以将载流子限制在量子阱中进行复合发光,保证发光效率。

[0067] 图3为本公开实施例提供的量子垒的势垒高度的结构示意图。参见图3,第一InGaN层的势垒包括高度依次减小的两个阶梯A和B,阶梯A的势垒高度可以为量子垒与量子阱的势垒高度之差的80%,阶梯B的势垒高度可以为量子垒与量子阱的势垒高度之差的50%;第二InGaN层的势垒C保持不变且等于量子垒与量子阱的势垒高度之差;第三InGaN层的势垒包括高度依次增大的两个阶梯D和E,阶梯D的势垒高度可以为量子垒与量子阱的势垒高度之差的80%。以量子垒与量子阱的势垒高度之差的80%。以量子垒与量子阱的势垒高度之差的80%。以量子垒与量子阱的势垒高度之差为基准,从量子垒到阶梯A,势垒高度下降20%;从阶梯A到阶梯B,势垒高度下降30%;从阶梯B到阶梯C,势垒高度下降50%;从阶梯C到阶梯D,势垒高度上升50%;从阶梯D到阶梯E,势垒高度上升30%;从阶梯E到量子垒,势垒高度上升20%。

[0068] 可选地,在通入反应腔内In源的流量增大时,In源流量的增大速率可以逐渐增大,使第一InGaN层的势垒高度减小处呈圆弧状。

[0069] 可选地,在通入反应腔内In源的流量减小时,In源流量的减小速率可以逐渐减小,使第三InGaN层的势垒高度增大处呈圆弧状。

[0070] 通过在改变通入反应腔内In源流量的同时,同步改变In流量的变化速率,减缓InGaN层的势垒高度的变化,使得InGaN层的势垒高度的变化处呈圆弧状,使得载流子能够较为平缓地通过量子阱,有效减缓量子阱对量子垒晶格的冲击,量子垒可以将载流子限制在量子阱中进行复合发光,保证发光效率。

[0071] 还是以图3为例,如图3所示,势垒高度从阶梯A减小至阶梯B的拐弯处、从阶梯B减小至阶梯C的拐弯处、从阶梯C减小至阶梯D的拐弯处、从阶梯D增大至阶梯E的拐弯处、从阶梯E增大至阶梯G的拐弯处均呈圆弧状。

[0072] 可选地,每个量子垒可以采用如下方式生长:

[0073] 向反应腔内通入A1源,生长A1GaN层。

[0074] 通过在量子垒的生长过程中通入A1源,形成势垒较高的A1GaN层,可以增大量子垒和量子阱之间的势垒高度之差,有利于量子垒将载流子限制在量子阱中进行复合发光,保证发光效率。

[0075] 在实际应用中,每个量子垒可以采用如下方式生长:

[0076] 向反应腔内通入Ga源和N源,生长GaN层。

[0077] 未掺杂杂质,晶体质量较好。

[0078] 可选地,半导体器件还可以包括透明导电层,透明导电层设置在空穴产生层和P型电极之间,一方面与电极之间形成良好的欧姆接触,另一方面对电极注入的电流进行扩展。示例性地,透明导电层的材料可以为氧化铟锡(英文:Indium tin oxide,简称:ITO)或者NiAu合金,透明导电层的厚度可以为2000埃。

[0079] 步骤102:将半导体器件转移到电路板上,每个发光单元中的P型电极键合在电路板的第一表面上。

[0080] 图4为本公开实施例提供的显示阵列在执行步骤102之后的结构示意图。参见图4, 多个发光单元40的P型电极21键合在电路板10同一个表面上, 即电路板10的第一表面。

[0081] 可选地,电路板可以包括依次层叠的基板、驱动电路和导热绝缘层。其中,基板提供支撑,驱动电路提供芯片的控制电路,导热绝缘层对芯片发光产生的热量进行散热,并将驱动电路与芯片绝缘,有利于驱动电路布线。

[0082] 在实际应用中,基板可以采用硅片,以便在基板上直接形成驱动电路;基板也可以采用碳化硅片或者陶瓷片,此时基板上可以制作硅、砷化镓等材料,以便形成驱动电路。驱动电路可以采用金属氧化物半导体场效应晶体管(英文:Metal-Oxide-Semiconductor Field-Effect Transistor,简称:MOS管)形成。导热绝缘层上设有延伸至驱动电路的通孔,通孔内填充有厚度大于3微米的金层。

[0083] 可选地,电路板的第一表面上可以设有与半导体器件一一对应的定位柱,定位柱平行于电路板的第一表面的截面的面积向远离电路板的第一表面的方向逐渐增大。

[0084] 相应地,该步骤102可以包括:

[0085] 将半导体器件放置在电路板的第一表面上,直到半导体器件中的P型电极与电路板的第一表面相贴;

[0086] 沿平行于电路板的第一表面的方向移动半导体器件,直到半导体器件与半导体器件对应的定位柱相抵;

[0087] 将半导体器件和电路板键合在一起。

[0088] 图5为本公开实施例提供的显示阵列在步骤102之后的俯视图。参见图5,半导体器件的衬底41与定位柱11相抵。

[0089] 通过在电路板上设置定位柱,可以引导半导体器件移动到指定位置处进行固定,而且定位柱的截面面积上面大下面小,有利于将半导体器件压在电路板上。

[0090] 示例性地,定位柱的材料可以采用氮氧化硅,实现成本低。

[0091] 通过在定位柱的形成过程中逐渐增大氮氧化硅中氮组分的含量,利用组分含量的不同带来的腐蚀速率的不同,腐蚀形成所需形状的定位柱。

[0092] 在实际应用中,半导体器件和电路板可以通过加热的方式键合在一起。

[0093] 步骤103:依次去除衬底和每个发光单元中的缓冲层,并在每个发光单元中的电子产生层上设置N型电极,形成发出第一颜色光线的芯片。

[0094] 图6为本公开实施例提供的显示阵列在执行步骤103之后的结构示意图。参见图6, 去除每个发光单元40中的衬底41和缓冲层42, 并在电子产生层24上设置N型电极25, 形成芯片20。

[0095] 在实际应用中,衬底可以采用激光剥离技术去除,缓冲层可以采用干法刻蚀技术去除,N型电极可以采用PVD技术形成。各个发光单元中的N型电极之间可以通过导线连接。可选地,导线与N型电极可以同时加工,以减少工序,降低实现成本。

[0096] 同一个半导体器件上发光单元的数量较少,激光剥离衬底时造成的损伤较小,可以改善激光剥离良率。

[0097] 可选地,该制作方法还可以包括:

[0098] 在电子产生层上铺设钝化保护材料:

[0099] 在钝化保护材料上形成设定图形的光刻胶;

[0100] 湿法腐蚀没有光刻胶覆盖的钝化保护材料,留下的钝化保护材料形成钝化保护层;

[0101] 去除光刻胶。

[0102] 示例性地, 钝化保护材料可以采用CVD技术铺设, 光刻胶可以采用光刻技术形成。

[0103] 步骤104:分别在不同的芯片上设置第一荧光粉层和第二荧光粉层,第一荧光粉层 将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为第三颜色光线。

[0104] 图7为本公开实施例提供的显示阵列在执行步骤104之后的结构示意图。参见图7,第一荧光粉层31和第二荧光粉层32分别设置在不同的芯片20上。

[0105] 示例性地,第一颜色光线可以为蓝光,第二颜色光线可以为红光,第三颜色光线可以为绿光。

[0106] 图8为本公开实施例提供的显示阵列在执行步骤104之后的俯视图。参见图8,四个芯片20阵列设置形成的Micro LED模块中,左上角的芯片20上设置第一荧光粉层31发红光,右上角和左下角的芯片20上设置第二荧光粉层32发绿光,右下角的芯片20上没有设置荧光粉层(露出电子产生层24)发蓝光,以满足显示需要。

[0107] 在实际应用中,可以在芯片10上涂布含有红光荧光粉的聚酰亚胺(英文: Polyimide,简称:PI)涂布液,图形化之后固化形成第一荧光粉层31;在芯片10上涂布含有绿光荧光粉的PI涂布液,图形化之后固化形成第二荧光粉层32。

[0108] 本公开实施例通过将多个发光单元集成在同一个衬底上一起转移到电路板上,衬底设置发光单元的表面上两点之间的最大距离为0.2mm~1mm,将转移的半导体器件的尺寸增大至比转移设备的吸嘴直径大,可以解决转移设备的吸嘴直径不能比Micro LED芯片的尺寸小的问题,使得转移设备可以提供足够的吸力转移Micro LED芯片。而且衬底设置发光单元的表面上两点之间的最大距离为0.2mm~1mm,设置在衬底上发光单元的数量较少,有利于保证设置位置的精确度。另外,多个发光单元一起转移到电路板上,可以减少转移的数量,降低加工成本。

[0109] 本公开实施例提供了一种微型发光二极管显示阵列。图9为本公开实施例提供的

一种微型发光二极管显示阵列的结构示意图。参见图9,该微型发光二极管显示阵列包括电路板10、多个芯片20、第一荧光粉层31和第二荧光粉层32,多个芯片20间隔设置在电路板10的第一表面上,每个芯片20包括依次层叠在电路板10的第一表面上的P型电极21、空穴产生层22、有源层23、电子产生层24和N型电极25,第一荧光粉层31和第二荧光粉层32分别设置在不同的芯片20上,芯片20发出第一颜色光线,第一荧光粉层31将第一颜色光线转换为第二颜色光线,第二荧光粉层32将第一颜色光线转换为第三颜色光线。

[0110] 可选地,如图9所示,电路板10的第一表面上可以设有定位柱11,定位柱11平行于电路板10的第一表面的截面的面积向远离电路板10的第一表面的方向逐渐增大。

[0111] 图10为本公开实施例提供的有源层的结构示意图。参见图10,可选地,有源层23包括交替层叠的多个量子阱231和多个量子垒232,每个量子阱231可以包括依次层叠的第一InGaN层231a、第二InGaN层231b和第三InGaN层231c,如图3所示,第一InGaN层231a的势垒高度沿生长方向梯度减小,第二InGaN层231b的势垒高度保持不变,第三InGaN层231c的势垒高度沿生长方向梯度增大。

[0112] 可选地,如图3所示,第一InGaN层231a的势垒高度减小处可以呈圆弧状。

[0113] 可选地,如图3所示,第三InGaN层231c的势垒高度增大处可以呈圆弧状。

[0114] 本公开实施例提供了一种微型发光二极管外延片。图11为本公开实施例提供的一种微型发光二极管外延片的结构示意图。参见图11,该微型发光二极管外延片包括衬底41和依次层叠在衬底41上的缓冲层42、电子产生层24、有源层23和空穴产生层22,如图10所示,有源层23包括交替层叠的多个量子阱231和多个量子垒232,每个量子阱231可以包括依次层叠的第一InGaN层231a、第二InGaN层231b和第三InGaN层231c,如图3所示,第一InGaN层231a的势垒高度沿生长方向梯度减小,第二InGaN层231b的势垒高度保持不变,第三InGaN层231c的势垒高度沿生长方向梯度增大。

[0115] 可选地,如图3所示,第一InGaN层231a的势垒高度减小处可以呈圆弧状。

[0116] 可选地,如图3所示,第三InGaN层231c的势垒高度增大处可以呈圆弧状。

[0117] 以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

图1

图2

图3

图4

图5

图8

图9

图10

图11

| 专利名称(译)        | 微型发光二极官外延片、显示阵列及具制作万法                                        |         |            |  |

|----------------|--------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | CN111180379A                                                 | 公开(公告)日 | 2020-05-19 |  |

| 申请号            | CN201911367573.7                                             | 申请日     | 2019-12-26 |  |

| [标]申请(专利权)人(译) | 华灿光电(苏州)有限公司                                                 |         |            |  |

| 申请(专利权)人(译)    | 华灿光电(苏州)有限公司                                                 |         |            |  |

| 当前申请(专利权)人(译)  | 华灿光电(苏州)有限公司                                                 |         |            |  |

| [标]发明人         | 兰叶<br>吴志浩<br>李鹏                                              |         |            |  |

| 发明人            | 兰叶<br>吴志浩<br>李鹏                                              |         |            |  |

| IPC分类号         | H01L21/683 H01L33/00 H01L33/62 H01L33/06 H01L33/32 B82Y40/00 |         |            |  |

| 外部链接           | Espacenet SIPO                                               |         |            |  |

少用尖坐一切管从延上 目示阵列及甘制作士法

#### 摘要(译)

**井利夕新/汉**)

本公开提供了一种微型发光二极管外延片、显示阵列及其制作方法,属于半导体技术领域。制作方法包括:提供半导体器件,半导体器件包括衬底和在衬底的第一表面上间隔设置的多个发光单元,衬底的第一表面上两点之间的最大距离为0.2mm~1mm;将半导体器件转移到电路板上,每个发光单元中的P型电极键合在电路板的第一表面上;依次去除衬底和每个发光单元中的缓冲层,并在每个发光单元中的电子产生层上设置N型电极,形成发出第一颜色光线的芯片;分别在不同的芯片上设置第一荧光粉层和第二荧光粉层,第一荧光粉层将第一颜色光线转换为第二颜色光线,第二荧光粉层将第一颜色光线转换为第三颜色光线,第二荧光粉层将第一颜色光线转换为第三颜色光线。本公开可转移Micro LED芯片。